What are the classifications of programmable logic devices?

PLD is a new type of logic device developed in the 1970s, and it is the main hardware basis for digital system design. According to the difference of programmable logic device structure, integration level, and programming technology, it has the following different classification methods.

There are mainly the following classification methods:

Classified by structural characteristics

Classified by programming process

Classification by integration

Classified by granularity

1. Classification according to structural characteristics

One is the device based on the "and-or" array structure-array type; (eg: PROM, EPROM, EEPRM, PAL, GAL, CPLD, EPLD, EPLA)

The second is the device based on the gate array structure-cell type; (such as FPGA)

1. Programmable read-only memory (PROM)

Programmable read-only memory is only allowed to be written once, so it is also called one-time programmable read-only memory. When the programmable read-only memory leaves the factory, the stored content is all 1, and the user can write data 0 in some of the units as needed (some PROMs have all 0 data when they leave the factory, and the user can set some of the units Write 1) to achieve the purpose of programming.

Typical PROM products are divided into two categories:

One type is a classic programmable read-only memory, which is a PROM using "Schottky diodes", which is a junction destruction circuit composed of diodes. When leaving the factory, the diode is in the reverse cut-off state, and the reverse voltage is applied to the "Schottky diode" with a large current to cause its permanent breakdown.

The other type is a fuse type circuit composed of transistors. If you want to rewrite some units, you can pass a large enough current to these units for a certain period of time, and the original fuse can be blown. Rewrite the effect of a certain person.

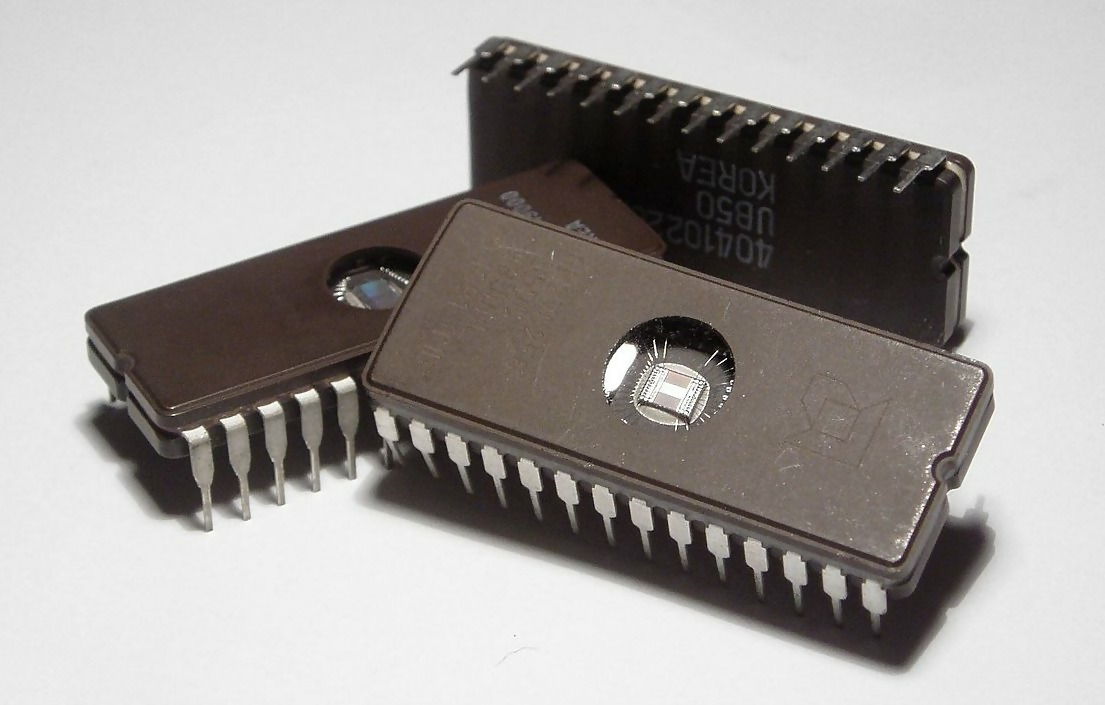

2.Erasable programmable read-only memory (EPROM)

The EPROM, which was first developed and put into use, was erased with ultraviolet light. EPROM adopts MOS type circuit structure, and its memory cell is usually composed of stacked gate type MOS transistors, while stacked gate type MOS transistors usually adopt enhanced field-effect transistor structure.

3. Electrically erasable programmable read-only memory (EEPROM)

EEPROM is a programmable ROM that is erased and rewritten with electrical signals. It can not only erase the memory cell content as a whole but also erase and rewrite word by word. The erasing and rewriting current of EEPROM is very small, and it can be carried out under normal working power supply, and there is no need to remove the device from the system when erasing.

4. Programmable Array Logic (PAL)

PLA follows the fuse type bipolar process used in the production of PROM devices. It has a programmable AND array and a fixed OR array structure, and can also achieve a very high working speed. Compared with PROM, PLA devices have greatly reduced array size and can realize various logic functions more flexibly. PLA devices are simple to program and have strong adaptability, and can replace many common small and medium-sized transistor logic devices.

5. General Array Logic (GAL)

GAL is an electrically erasable and reprogrammable logic device. It has a flexible programmable output structure so that the few centralized GAL devices can replace almost all PAL devices and hundreds of small and medium-sized standard devices. Moreover, GAL adopts advanced EECMOS technology, which can complete the erasing and writing of the device within a few seconds, and allows repeated rewriting. Ordinary GAL devices and PAL devices have the same array structure, and both adopt an AND array programmable or fixed array structure.

6. Complex programmable logic device (CPLD)

CPLD is a large-scale integrated programmable logic device developed on the basis of PAL, GAL, and other devices. Compared with PAL, GAL, and other devices, the scale of CPLD is relatively large. One CPLD can replace dozens or even hundreds of general-purpose devices. IC chip. Although the CPLD mechanisms produced by different IC companies are very different, they generally include three parts: programmable logic macro unit, programmable I/O unit, and programmable internal wiring.

7. Erasable programmable logic device (EPLD)

EPLD combines the advantages of large-scale integrated circuits such as small size, low price, and high reliability. Users can design special circuits according to their needs to avoid problems such as high prices and long cycles. The delay time of EPLD devices is predictable and fixed. Therefore, any function implemented on the function template in the EPLD device has the same speed. The functional modules are interconnected through unlimited internals, providing multiple programmable logic structures. And each functional module contains 9 programmable "and" "or" array-driven macrocells, the input of anyone pin or the output of the macro cell can be connected to the input of another macrocell, this kind of unlimited The programming interconnect structure ensures that the EPLD has 100% wiring capacity.

8. Field Programmable Logic Array (FPLA)

Field Programmable Logic Array (FPLA) is a type of Programmable Logic Device (PLD), which is a semiconductor device that contains the so-called "logic block" and programmable interconnects in programmable logic elements. Logic blocks are programmed to perform basic logic gate functions, such as "and" "exclusive OR" or more complex combination functions. In most FPLAs, logic blocks also include memory molecules and hierarchical programmable interconnects to meet the need for logic blocks to be interconnected. In addition, the structure of FPLA is similar to that of ROM. The difference is: first, ROM and array are fixed, while FPLA and array are programmable; secondly, ROM and array output are all the smallest items, while FPLA and array You can output a simplified expression. The system designer performs any logic function according to the customer or designer's needs, so it is named "field-programmable".

9. Field programmable gate array (FPGA)

FPGA is further developed on the basis of PAL, GAL, CPLD, and other programmable devices. It is a device based on the cell gate array structure. Because FPGA needs to be burned and written repeatedly, its basic structure for realizing combinational logic cannot be completed by a fixed NAND gate like ASIC, but can only adopt a structure that is easy to repeatedly configure. At present, mainstream FPGAs all use look-up tables based on SRAM technology, and some military supplies and aerospace-grade FPGAs use look-up table structures of Flash or fuse and anti-fuse technology. The method of changing the contents of the look-up table can be achieved by burning files. Repeated configuration of FPGA.

According to the Boolean algebra theory, for a logical operation with n inputs, no matter it is an AND or NOT operation, there may only be 2n results at most, so if the corresponding result is first stored in a storage unit, it is equivalent to achieving NAND. The function of the gate circuit. The principle of FPGA is also the same. It configures the contents of the lookup table by programming files, thereby realizing different logic functions in the same circuit.

2. Classified by programming process

1. Fuse and Antifuse programming devices

It is a non-volatile original for one-time programming. Even if the system is powered off after programming, the stored programming information will not be lost.

2. SRAM type device

Most of the company's FPGA devices are SRAM devices, which can be repeatedly programmed to achieve dynamic reconfiguration of system functions. However, it needs to be re-downloaded every time the power is turned on, and an external EEPROM is required to save the program in actual application.

3. Programmable read-only memory devices with erasable electrical signals are volatile devices. Most CPLD devices are EEPROM devices, which can be programmed repeatedly without re-downloading each time the power is turned on, but they are relatively slow and consume more power.

4. Erasable programmable read-only memory programming devices are volatile devices.

Three, according to integration

1. Low-density programmable logic devices

The integration level is below 1000 doors. Early programmable logic devices, such as PROM, PLA, PAL, GAL, etc., can only complete small-scale logic circuits, so they are all low-density devices.

2. High-density programmable logic devices

The integration level is more than 1000 gates. The popular EPLD, CPLD, and FPGA are high-density devices, which can be used to design large-scale digital systems, and even system on chip (System on Chip, SoC) design.

4. Classification by granularity

1. Small granularity, such as Haimen architecture.

2. Medium granularity, such as FPGA

3. Large particle size, such as CPLD

The electronic components mentioned above can be found on Jotrin's official website.